计组第一次小测笔记

-

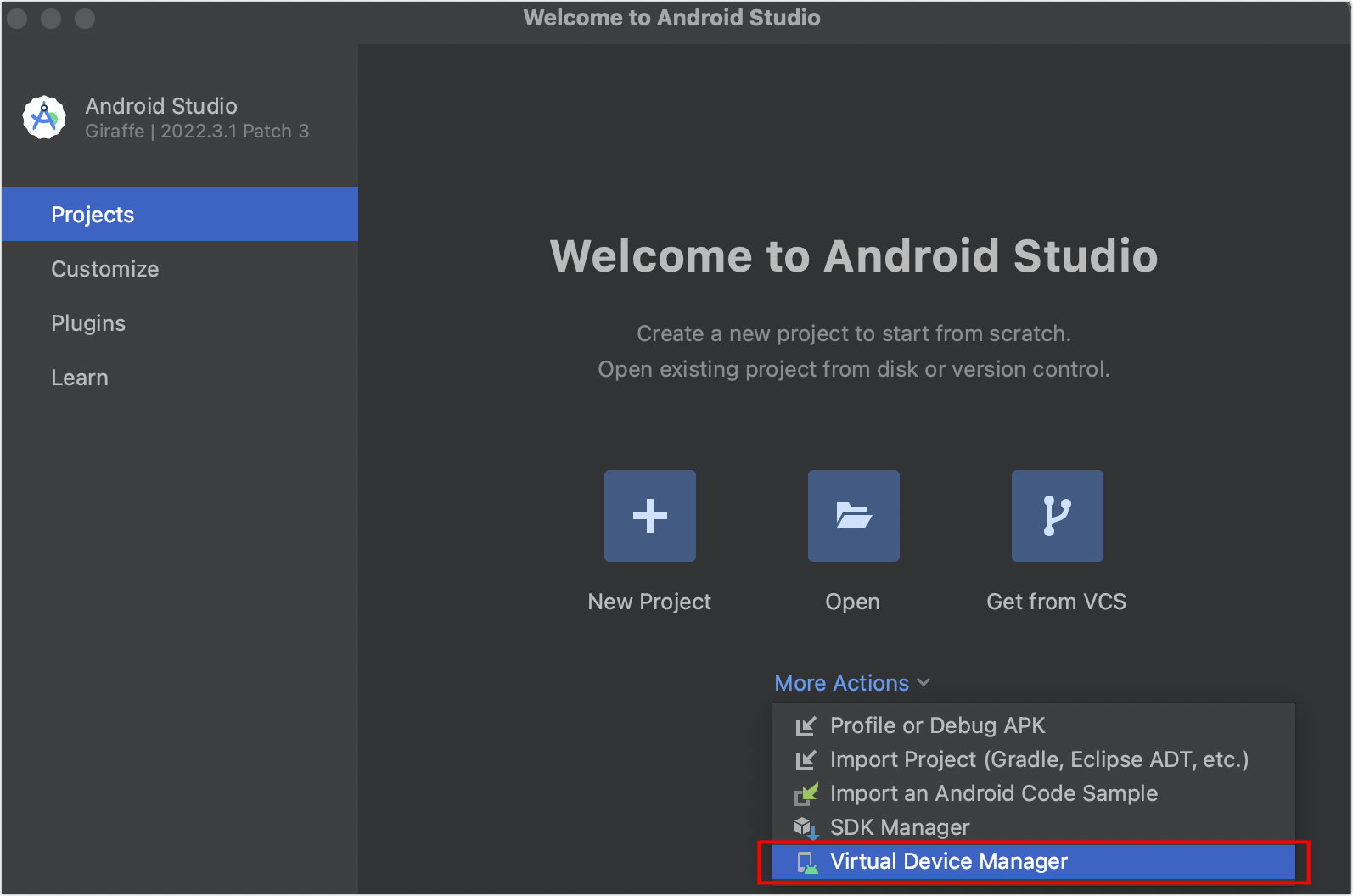

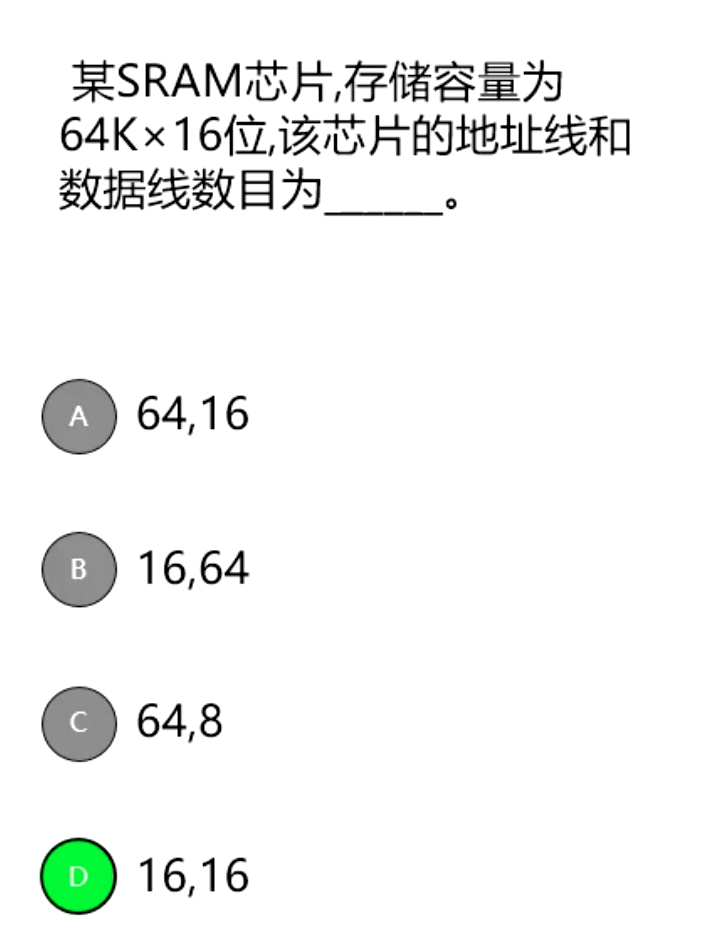

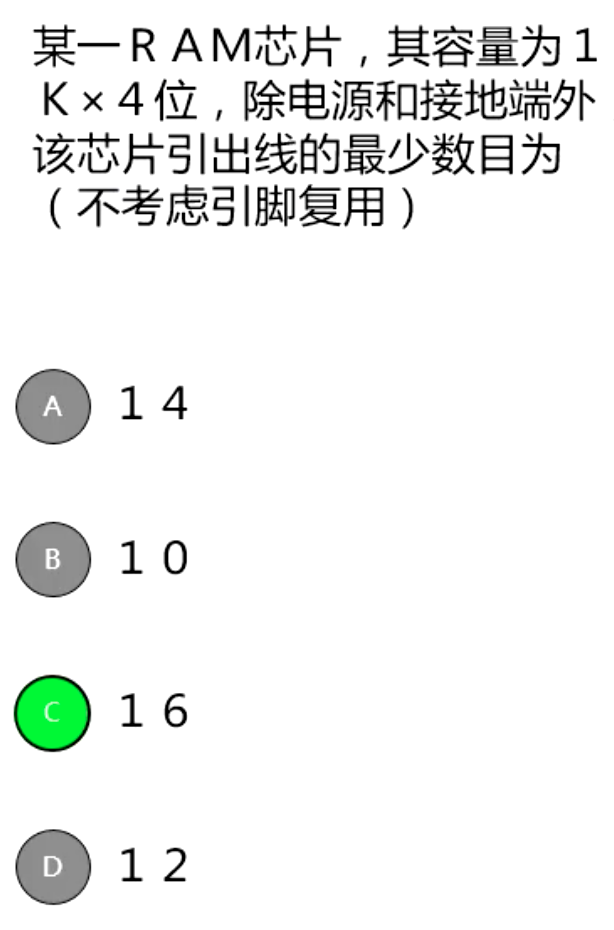

如图,解析:2^16 + 16

-

CPU组成不包括寄存器

-

Cache全相联映射

-

PCI是与处理器无关的高速外围总线

-

CU不是寄存器,ACC累加寄存器 IR指令寄存器 MQ乘商寄存器

-

片内总线不是系统总线,系统总线包括地址、数据、控制线

-

总线忙信号BS的建立者是 获得总线控制权的设备

-

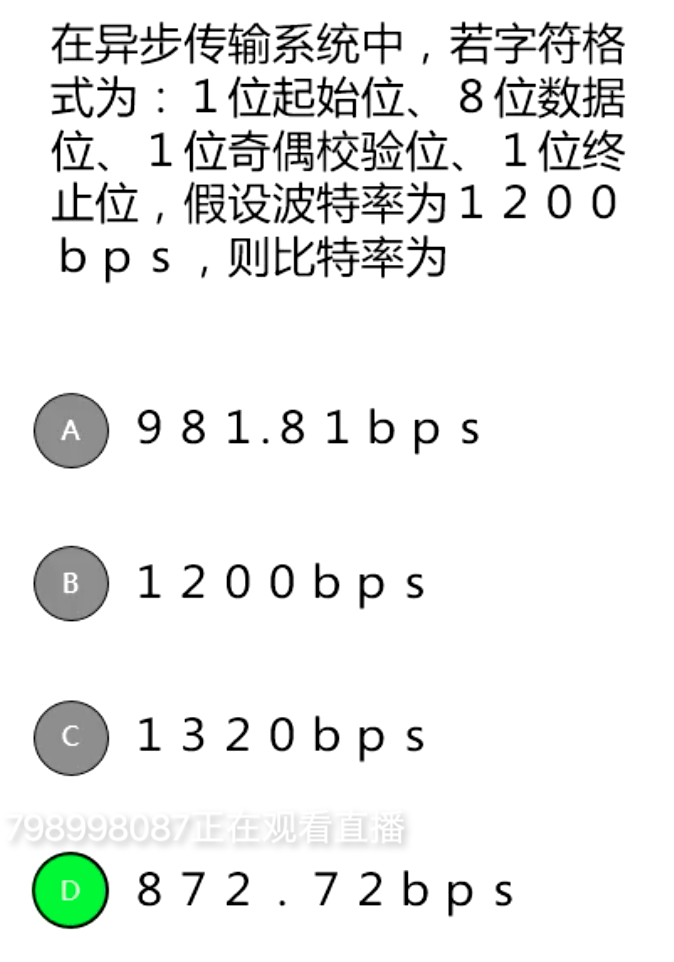

如图,波特率*8/11 = 比特率

-

-

假设缓存的工作速度为主存的5倍,缓存的命中率为90%,则采用缓存后,存储器的性能是原来的()倍

答:3.57

-

CPU中跟踪指令后继地址的寄存器是:

答:PC

-

完整的计算机硬件系统包括

答:外部设备和主机

-

总线的半同步通信方式特点:

答:既采用时钟信号(同步特点),又采用应答信号(异步特点)

-

总线复用可以:

答:减少总线中信号线数量

-

在计数器定时查询方式下,若每次计数器从上一次计数的终止开始,则:

答:每个设备使用总线机会相等

-

连接计算机与计算机之间的总线属于:

答:通信总线

-

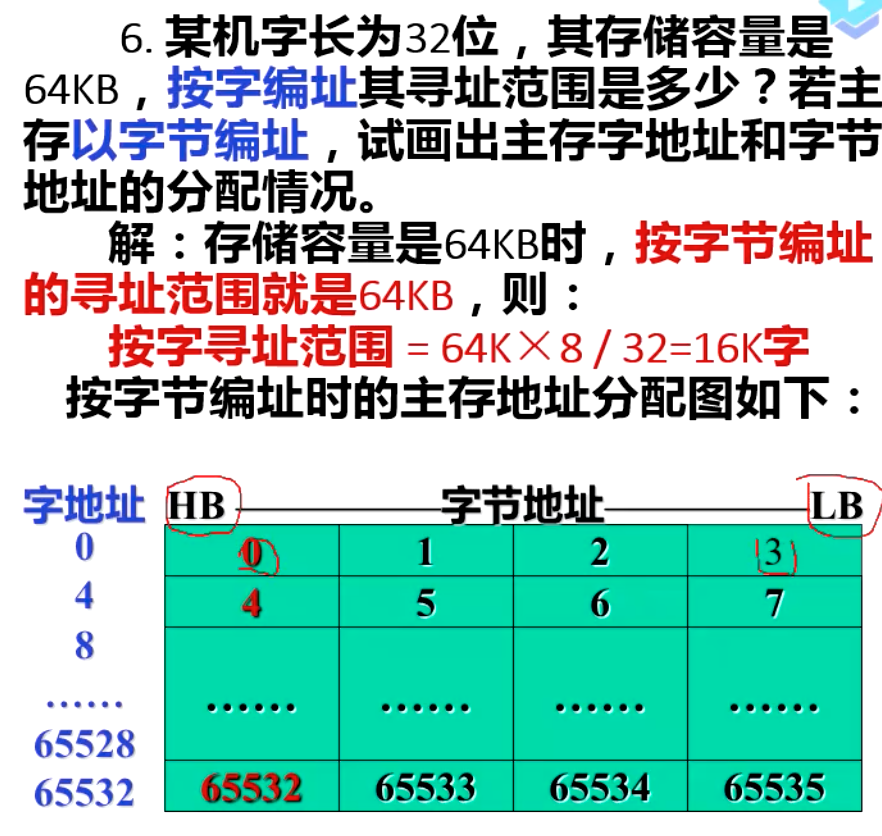

某计算机字长是16位,它的存储容量是64KB,若按字编址,寻址范围是:

答:32K

16位为两个字节 64k*8 bit/2 = 32K

拓展:

-

一个256KB的存储器,按字节编制,其地址线和数据线的总和是:

答:26

-

DRAM的刷新是以行为单位

-

设CPU地址总线有24根数据总线有32根,用512Kx8位的RAM芯片构成该主机的存储器,则需要( )片

答:128片

-

某计算机的CaChe共有32块,采用二路组相联映射方式。每个存储块大小为32字节,按字节编址,主存第2001号字节所在的主存块应装入Cache组号是:

答:14

主存块号 mod cache组数

2001/32 = 62余17 可推出主存在63块,但由于主存块号从0开始计算,则主存块号为62

则62 mod 16组 = 14

-

用若干个2Kx4位的芯片组成一个8Kx8位存储器,则1634H所在芯片的最小地址是:

答:1000H

拓展:求最大地址

-

有效容量为128KB的缓存每块为16字节,采用8路组相联。字节地址为1234567H的单元调入该缓存,则其标记Tag为:

答:048DH

把字节地址转为二进制,共有7*4=28位

三块分别表示为:28-14=14,组数信息10,位数4

128/16*8=2^10,则组数信息为10;由2^4=16,则位数为4

-

若片选地址为101时(地址线的高位),选定某一32K*16的存储芯片工作,则该芯片在存储器中的首地址和末地址分别为:

答:28000H, 2FFFFH

关键是32K -> 芯片内部地址线为15根 片内地址a0-a14,高位a15 a16 a17是101时求解题目

-

存放在寄存器ACC中的操作数有:

答:被除数及余数、被加数及和

-

关于Cache的写操作中的 “写直达法”

答:写操作时,数据既写入缓存又写入主存,写操作的时间等于访问主存的时间。

-

DRAM常用刷新方式:集中、分散、异步